Multiple Choice

Identify the

choice that best completes the statement or answers the question.

|

|

|

1.

|

The data storage device which

can be constructed using two NAND gates or two NOR gates is the

a. | encoder. | c. | S-R flip-flop. | b. | J-K flip-flop. | d. | multiplexer. |

|

|

|

2.

|

The input combination that

drives the output of a NOR gate S-R flip flop to Q = 1 and  = 0 is

________. = 0 is

________.

a. | S = 1, R =

1 | c. | S = 1, R =

0 | b. | S = 0, R =

0 | d. | S = 0, R = 1 |

|

|

|

3.

|

The input combination that

drives the output of a NOR gate S-R flip-flop to Q = 0 and  = 1 is

________. = 1 is

________.

a. | S = 0, R =

1 | c. | S = 1, R =

1 | b. | S = 1, R =

0 | d. | S = 0, R = 0 |

|

|

|

4.

|

The input combination that

drives the output of a NOR gate S-R flip-flop to Q = 0 and  = 0 is

________. = 0 is

________.

a. | S = 1, R =

1 | c. | S = 0, R =

1 | b. | S = 0, R =

0 | d. | S = 1, R = 0 |

|

|

|

5.

|

When a flip-flop is SET,

________.

a. | Q and  =

1 =

1 | c. | Q =

0 | b. |  =

1 =

1 | d. | Q = 1,  =

0 =

0 |

|

|

|

6.

|

When a flip-flop is RESET,

________.

a. | Q = 1,  =

0 =

0 | c. | Q = 0,  =

0 =

0 | b. | Q = 0,  =

1 =

1 | d. | Q =  |

|

|

|

7.

|

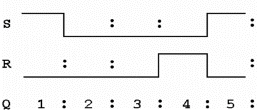

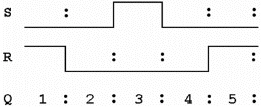

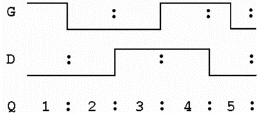

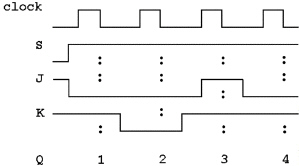

The waveforms below represent

the inputs to a S-R flip-flop. During which time interval(s) will the Q output of the flip-flop be

LOW?

|

|

|

8.

|

The waveforms below represent

the inputs to a S-R flip-flop. During which time interval(s) will the Q output of the flip-flop be

HIGH?

|

|

|

9.

|

A gated S-R flip-flop can be

constructed from two AND gates and two NOR gates or from

a. | four AND

gates. | c. | four OR

gates. | b. | four NOR gates. | d. | four NAND gates. |

|

|

|

10.

|

A gated S-R flip-flop goes into

the SET condition when

a. | S is LOW

R is HIGH

Enable is

LOW | b. | S is HIGH

R is HIGH

Enable is HIGH | c. | S is HIGH

R is LOW

Enable is

HIGH | d. | S is HIGH

R is LOW

Enable is

LOW |

|

|

|

11.

|

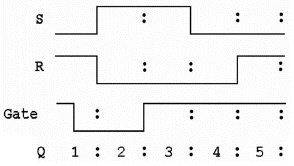

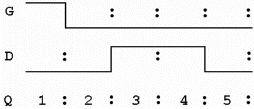

The waveforms below represent

the inputs to a gated S-R flip-flop. During which time interval(s) will the Q output of the flip-flop

be HIGH?

|

|

|

12.

|

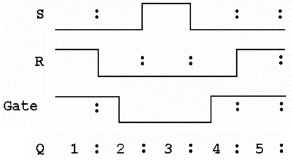

The waveforms below represent

the inputs to a gated S-R flip-flop. During which time interval(s) will the Q output of the flip-flop

be HIGH?

a. | 1 | c. | 3 and 4 | b. | 3 | d. | It will not be HIGH. |

|

|

|

13.

|

Which flip-flop has no invalid

or unused state?

a. | gated S-R

flip-flop | c. | D

latch | b. | S-R flip-flop | d. | NAND flip-flop |

|

|

|

14.

|

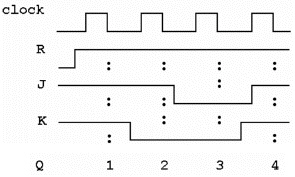

The waveforms below represent

the inputs to a D latch. During which time interval(s) will its Q output be HIGH?

a. | 4 and 5 | c. | 4 | b. | 3 and 4 | d. | 1 and 2 |

|

|

|

15.

|

The waveforms below represent

the inputs to a D latch. During which time interval(s) will its Q output be HIGH?

a. | 3, 4, and

5 | c. | 3 and

4 | b. | 1 | d. | It will not be HIGH. |

|

|

|

16.

|

An edge-triggered flip-flop can

only change states when

a. | the D input is

HIGH. | c. | the trigger input changes

levels. | b. | the trigger is HIGH. | d. | the trigger is LOW. |

|

|

|

17.

|

Which of the following

flip-flops have synchronous inputs?

a. | 7474

D-flip-flop | c. | S-R

flip-flop | b. | NAND flip-flop | d. | all of the above |

|

|

|

18.

|

An input which can only be

accepted when an enable or trigger is present is called

a. | RESET. | c. | asynchronous. | b. | synchronous. | d. | data. |

|

|

|

19.

|

The inputs on a 7474 D

flip-flop are S, R, D and clock. Which of these are asynchronous?

a. | S and R | c. | only S | b. | only D | d. | all of the above |

|

|

|

20.

|

A master-slave flip-flop

is

a. | asynchronous. | c. | edge-triggered. | b. | level-triggered. | d. | a new design. |

|

|

|

21.

|

The logic states of a J-K

flip-flop are SET, RESET, HOLD, and

a. | ENABLE. | c. | TOGGLE. | b. | TRIGGER. | d. | CLEAR. |

|

|

|

22.

|

TOGGLE state of a J-K flip-flop

means that the Q and  outputs will outputs will

a. | switch to Q = 1 and  = 0.

= 0. | c. | switch to

zero. | b. | switch to their opposite state. | d. | become the same as J and K. |

|

|

|

23.

|

If the inputs of a J-K

flip-flop are J = 1 and K = 1 while the outputs are Q = 0 and  = 1, what

will the outputs be after the next clock pulse occurs? = 1, what

will the outputs be after the next clock pulse occurs?

a. | Q = 1,  =

0 =

0 | c. | Q = 1,  =

1 =

1 | b. | Q = 0,  =

0 =

0 | d. | Q = 0,  =

1 =

1 |

|

|

|

24.

|

If the inputs of a J-K

flip-flop are J = 0 and K = 0 while the outputs are Q = 0 and  = 1, what

will the outputs be after the next clock pulse occurs? = 1, what

will the outputs be after the next clock pulse occurs?

a. | Q = 0,  =

1 =

1 | c. | Q = 0,  =

0 =

0 | b. | Q = 1,  =

1 =

1 | d. | Q = 1,  =

0 =

0 |

|

|

|

25.

|

If the inputs of a J-K

flip-flop are J = 1 and K = 0 while the outputs are Q = 0 and  = 1, what

will the outputs be after the next clock pulse occurs? = 1, what

will the outputs be after the next clock pulse occurs?

a. | Q = 0,  =

1 =

1 | c. | Q = 0,  =

0 =

0 | b. | Q = 1,  =

1 =

1 | d. | Q = 1,  =

0 =

0 |

|

|

|

26.

|

The symbol used on logic

diagrams for an edge-triggered clock input is

a. | a small

circle. | c. | a small

triangle. | b. | a small arrow. | d. |  |

|

|

|

27.

|

A negative edge-triggered

flip-flop will only accept inputs when the clock

a. | is

HIGH. | c. | changes from LOW to

HIGH. | b. | is LOW. | d. | changes from HIGH to LOW. |

|

|

|

28.

|

A positive edge-triggered

flip-flop will only accept inputs when the clock

a. | is

HIGH. | c. | is

LOW. | b. | changes from LOW to HIGH. | d. | changes from HIGH to LOW. |

|

|

|

29.

|

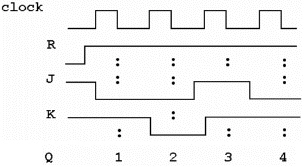

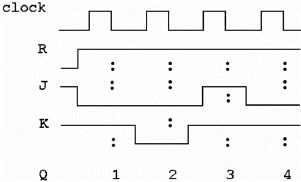

The waveforms below represent

the inputs to a negative edge-triggered J-K flip-flop. At which point(s) will its Q output go

HIGH?

a. | point 1 | c. | point 3 | b. | point 2 | d. | points 3 and 4 |

|

|

|

30.

|

The waveforms below represent

the inputs to an negative edge-triggered J-K flip-flop. At which point(s) will its Q output go

HIGH?

a. | point 3 | c. | points 3 and 4 | b. | point 4 | d. | point 2 |

|

|

|

31.

|

What will happen to the output

from a negative edge-triggered J-K flip-flop at point 2 of this timing diagram?

a. | It will

HOLD. | c. | It will

RESET. | b. | It will SET. | d. | It will TOGGLE. |

|

|

|

32.

|

What will happen to the output

from a negative edge-triggered J-K flip-flop at point 1 of this timing diagram?

a. | It will

TOGGLE. | c. | It will

SET. | b. | It will RESET. | d. | It will HOLD. |

|

|

|

33.

|

If data is brought into the J

terminal and its complement to the K terminal, a J-K flip-flop operates as a(n)

a. | gated S-R

flip-flop. | c. | S-R

flip-flop. | b. | D flip-flop. | d. | TOGGLE flip-flop. |

|

|

|

34.

|

A flip-flop is in the SET

condition when ________.

a. | Q = 0,  =

1 =

1 | c. | Q = 1,  =

0 =

0 | b. | Q =

0 | d. | Q and  change to opposite

states. change to opposite

states. |

|

|

|

35.

|

A flip-flop is in the RESET

condition when ________.

a. | Q = 1 | c. | Q = 0,  =

1 =

1 | b. | Q and  change to

opposite states. change to

opposite states. | d. | Q = 1,  =

1 =

1 |

|

|

|

36.

|

Inputs which cause the output

of a flip-flop to change instantaneously are

a. | edge-triggered. | c. | triggered. | b. | asynchronous. | d. | synchronous. |

|

|

|

37.

|

Which of the following is

not a name used with

flip-flops?

a. | gate | c. | memory | b. | register | d. | latch |

|

|

|

38.

|

Circuits that operate

sequentially, in step with a control input are called

a. | asynchronous. | c. | synchronous. | b. | memory. | d. | latching. |

|

|

|

39.

|

Which type of flip-flop uses

only one input to both Set and Reset?

|

|

|

40.

|

Which type of flip-flop is

referred to as "one's catching"?

|

|

|

41.

|

The inputs to a J-K flip-flop

are J=1 and K=1. The outputs are Q=1 and  =0. What will the outputs be after the next

clock pulse occurs? =0. What will the outputs be after the next

clock pulse occurs?

a. | Q=1,  =0 =0 | c. | Q=0,  =1 =1 | b. | Q=1,  =1 =1 | d. | Q=0,  =0 =0 |

|

|

|

42.

|

The inputs to a J-K flip-flop

are J=1 and K=0. The outputs are Q=1 and  =0. What will the outputs be after the next

clock pulse occurs? =0. What will the outputs be after the next

clock pulse occurs?

a. | Q=1,  =1 =1 | c. | Q=0,  =0 =0 | b. | Q=1,  =0 =0 | d. | Q=0,  =1 =1 |

|